WinlabMadwifi → Pipeline MAC paper Discussion

Paper Title:

Cooperative Scheduling Via Pipelining in 802.11 Wireless Networks

Download pdf

Ramana Rao Kompella, Sriram Ramabhadran, Ishwar Ramani, Alex C. Snoeren

University of California, San Diego

Motivation

- Per packet Micro-scheduling need firmware/hardware(MAC) upgrade

- Macro-scheduling could be done in multiple packet basis periodically, e.g 10ms.

- Cooperative scheduling extensions can be supported using a new layer on top of the existing MAC layer.

Features of Scheme

- each node conducts "global scheduling" based on "load information" of all other nodes.

- the global scheduling determines a TDMA-like slot/bandwidth allocation

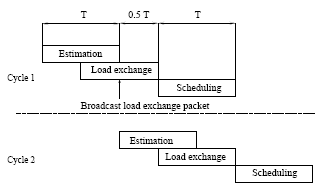

- 3 stages, 2 ½ pipelining:

- Estimation — load exchange — scheduling

- equivalent to predict — signaling — access

- "load excange" phase overlapping with "estimation"

- First cycle's scheduling overlap with second cycle's "load exchange" phase

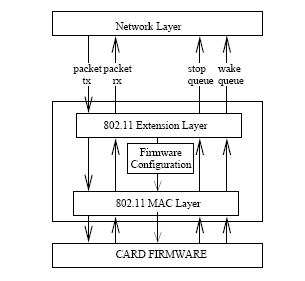

- Kernel code modification

- packet_tx

- packet_rx

- stop_queue

- wake_queue

Diagrams

Figure 1: 802.11 extension layer architecture

Figure 2:2.5-stage pipeline architecture. Each pipeline stage is equal in duration, but estimation stage and load exchange stage for a given cycle overlap with each other.

Experiment Evaluation

using 2 nodes and 1 AP, configure 1 node to have twice bandwidth as another node (interferer/competitor). All use NETGEAR cards (Atheros-chip).

Weakness

- a solution for IEEE 802.11 Wireless LAN, not a solution for multi-hop

- no solution for signalling loss, wrong scheduling automatically fades out in next cycle.

- rely on AP's beacon to sync all nodes.

- very simple experiment scenario and incomplete results.

Disucussion

- Is a kernel patch a good approach? The kernel & driver are difficult to develop. As long as the software can be stablized, it is a feasible approach.

- 10ms scheduling resolution, good enough? No. Schedule too many packets in a batch. It's better to use HW timer, a 64-bit timing counter in Atheros chip.

Last modified

20 years ago

Last modified on Feb 28, 2006, 12:45:38 PM

Attachments (2)

- pipelinefig1.png (8.8 KB ) - added by 21 years ago.

- pipelinefig2.png (5.8 KB ) - added by 21 years ago.

Download all attachments as: .zip

Note:

See TracWiki

for help on using the wiki.